LDO short form for Linear Drop-Out Regulator is one of the simplest power circuit design in Embedded Systems. The low drop out means there is low potential drop across the regulator which meant the difference between input and output is low, example in terms of milli volts. So, when say low drop out, the power loss is also getting lower and this relates to the low heat dissipated across the regulator. While the circuit looks simple, there are some considerations to be taken while designing the LDO circuit. It is always recommended to follow guidelines as per datasheet but th datasheet doesn't say everything. It is the designer who has to step into the shoes of application requirements and design accordingly.

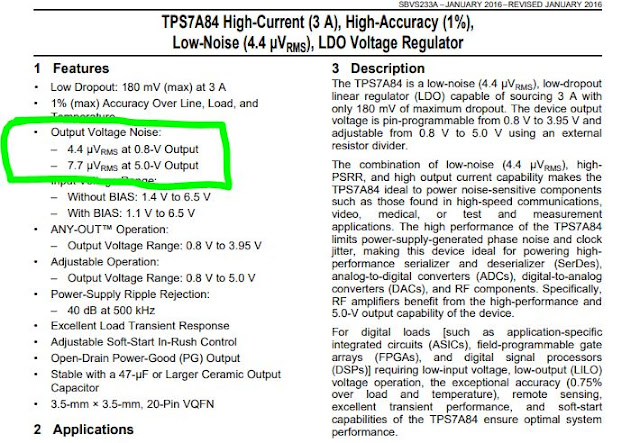

Let us take an example of TPS7A84, which is a LDO from Texas Instruments.

Talking about the internal circuit:

Similar to any other LDO, TPS7A84 has a pass element (MOSFET), Error Amplifier, feedback path, power good. While most of the LDO in the market must use external resistor divider network, TPS7A84 provides standard resistor configuration inside for generating a required output voltage.

The above resistor configuration at the output feedback path indicates one design consideration. While designing any feedback circuit, it is common approach to keep one resistor constant and vary the other resistor to generate the require voltage. One of the major disadvantage while selecting the resistors is that accurate value cannot be found. The internal resistors eliminates that scenario and also help to reduce the board space.

Consideration while designing a circuit around any LDO:

- Designer has to use the recommended input and output capacitors for stable operation of the LDO. Any deviation from these capacitors might vary the loop bandwidth and causing variation in transient response. The transient response is the maximum allowable output voltage variation for a load current step change.

- It is very important to control the rise time of output and limit the in-rush current, in such scenarios prefer to use soft-start.

- Prefer to use LDOs with MOSFET based pass element. These devices have lower power consumption

- If any condition demands where a designer has to increase the output capacitance of the LDO, correspondingly input capacitance has to be increased

- Bypass capacitors to be used at the output of the LDO for improved transient response. It is always preferred to use Ceramic capacitors with X5R/X7R dielectrics

- Considering the specification of TPS7A84 LDO, output noise is mentioned. This noise is mainly generated due to voltage reference generator.

- PSRR - The ability of regulator to prevent the output voltage variations due to variations in input voltage. Select a regulator with good PSRR.

- The efficiency of LDO is calculated using,

- The dropout voltage of the LDO is calculated using,

0 Comments