Impedance matching is one of the important consideration that need to be considered when we design circuits. As we design circuits much higher speeds, checking for impedance matching is a must. So, when we talk about impedance matching, what are all the considerations to be taken into account? Some of them are output impedance of the transmitter, input impedance of the receiver, trace impedance PCB characteristics.As the PCB design is a separate entity by itself, let us initially focus on the circuit design where the impedance plays a major role. So, when we talk about the impedance it is the impedance of the output buffer we are talking about or the input buffer. It is always important to understand the buffer characteristics of the respective interfaces/devices before we could design any circuit. This brings us to a long list of characteristics and logic levels is one of the most important. The selection of a specific chip depends on the logic levels supported by that chip set and

compatibility with the other chips on the board. So, if we try to list down the logic levels, we list

1. TTL

2. LVDS

3. CMOS

4. PECL

5. LVCMOS

6. LVCMOS

7. CML and so on

There are indeed different logic levels and we tried to list down the few here. Ensuring that correct clock output level is selected for a given application lies at the discretion of the circuit designer.

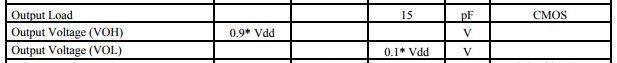

Take an example of ASE series oscillators from ABRACON. This is a CMOS based oscillator. The oscillator vendors clearly mention the logic level type which the output drives the load, so, design engineers need not even bother looking at the output levels and determine the type of logic level. The datasheet mentions about following parameters which are very important in determining the load that cn be connected.

1. Logic levels

a. Output voltage LOW (VOH)

b. Output voltage HIGH (VIH)

2. Load capacitance in pico Farad (pF)

0 Comments